The Allegro PCB Editor 16.6-2015 release provides Shape Edit Application Mode, a tuned editing environment optimized for the manipulation of shape boundaries.

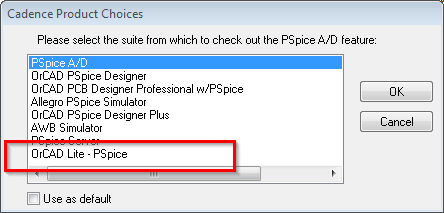

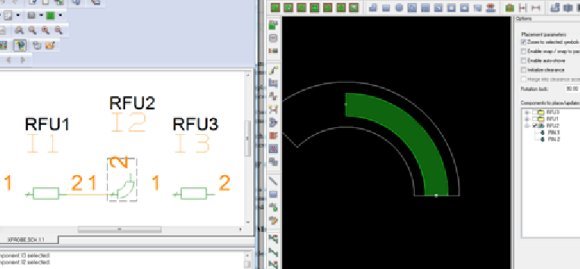

In SPB16.0, all Allegro back-end tools with the exception of the PCB Router were enhanced to support a new pre-selection editing model; this involves the selection or hover-over of an element followed by command action. This model is commonly referred to as “Noun-Verb” in the industry. Hover-over data tips, context-sensitive RMB popup menu, automatic execution of commands with a LMB pick, and quick access to associated parameter options are attributes of the enhanced editing environment designed to maximize productivity in design canvas while reducing mouse travel to the toolbar or control panel. It’s important to note that there are commands available in Application modes such as Placement and Shape Edit that are not available in the legacy editing mode.

New functionality designed to improve the user’s experience editing shape boundaries includes:

- The sliding of shape edges with or without corners

- Corner conversion

- Multi-segment sliding and the adding of notches

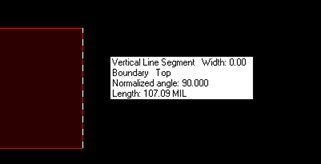

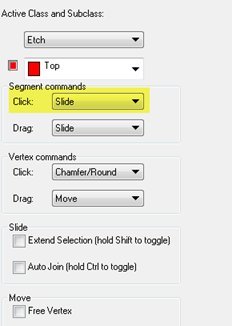

When entering the Shape Edit App Mode, note the Option Panel supports command options that accelerate the editing of the boundary. A LMB click or Drag is the recommended method to perform the essential shape edit functions:

![]()

Sliding a Segment (Shape Edge)

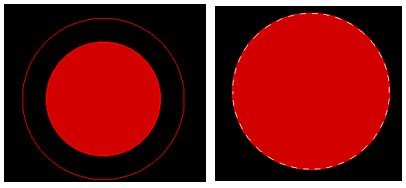

Hover over the right side shape edge as shown below. Your datatip may look different than what is displayed. Use the Tab key to cycle between the “segment” and “shape” element. After pressing the Tab key a few times, finalize with the “vertical line segment” being highlighted as shown below:

![]()

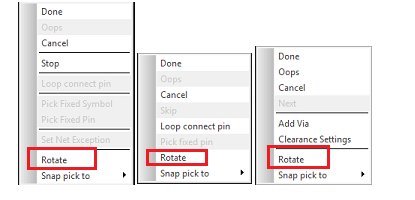

While hovering over the highlighted line segment, use the RMB to access the Slide Segment command. Slide the segment towards the right, then make a LMB pick in black space to clear the selection buffer.

Next we use an accelerated method to perform the same function. Refer to the Options Panel and note the settings for “Click” and “Drag”. With ‘Drag” currently set to “Slide”, hover over the same shape segment, then depress your LMB to slide it:

![]()

Change the “Click” value from Add Notch to Slide. Simply make a LMB pick on the segment to slide it. Similar behavior in Etch Edit Application mode for sliding segments.

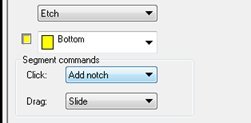

Perform any of the above steps on a Circular shape:

![]()

Extended Segment Slide

Enable the option “Extend Selection”. You can also use the SHIFT key to toggle the state of the “Extend Selection” option if you prefer:

![]()

Select the straight section of the shape edge as shown below. Ensure the segment is highlighted as you begin to hover over it, then slide it, noting how the corners are maintained during the dynamics:

![]()

Disable the “Extend Selection” option and slide the segment, noting the behavior is limited to just the single segment:

![]()

Perform the same steps to slide the edge of the rounded rectangle that is located to the right of the chamfered rectangle:

![]()

Adding a Notch

Adding a notch is a two-step process where you select two points on a straight segment and extend inward or outward. The example below is an “inward” notch:

![]()

Hover over the bottom segment, then use the RMB to access the Add Notch command. Position the two white squares that define the notch width, then move your cursor to define the notch length:

![]()

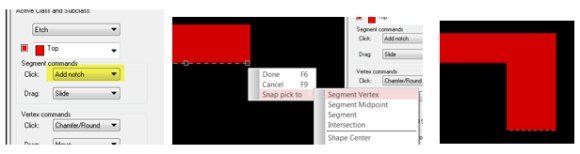

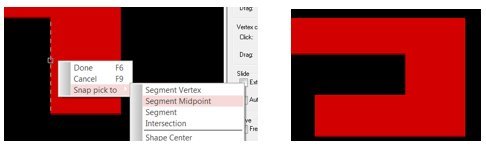

Use “single-click execution” mode to add the next notch. Ensure the “Click” option is set to “Add Notch”. Based on the figures below, make your first LMB pick, then use RMB – Snap Pick to – Segment Vertex to add the second pick directly at the corner vertex location:

![]()

Add one more notch using the RMB – Add Notch method. Hover over the inside segment as shown in the left figure below, then use RMB - Snap Pick to – Segment Midpoint to place the first point at the midpoint of the segment. Add the second notch at the corner using RMB – Snap Pick to – Segment Vertex:

![]()

Move Vertex

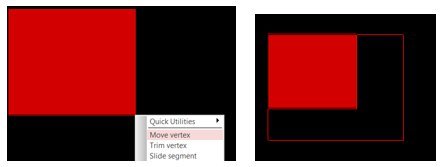

Selecting a vertex location on a shape boundary performs a two-segment move. Hover over the lower right corner of the shape, you will notice the change in style of the cursor. Use the RMB to access the Move Vertex command. Move your cursor to increase the shape width and length:

![]()

Perform the same action using a single LMB click or DRAG based on the “Vertex commands” setting shown below. Click on one of the inside boundaries of the notched shape and extend upwards and also to the right:

![]()

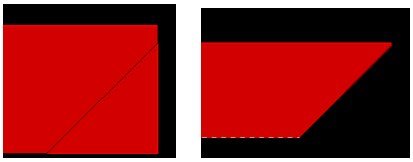

Chamfering Corners

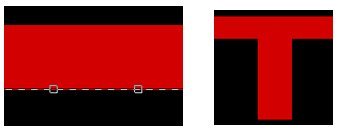

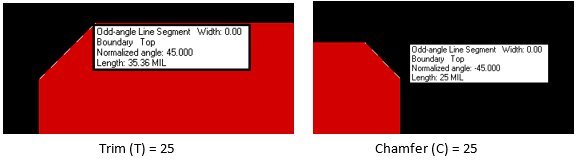

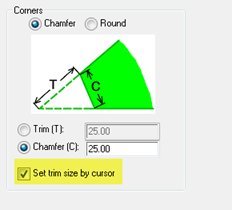

Adjust the settings as shown in the figure below. Hover over the top left corner then use the RMB to access the Trim Vertex command. Referring to the bitmap “T”, a value of 25 produces a 35.36 chamfered length - [Square root of (25 squared + 25 squared)] = 35.36:

![]()

Change the setting from Trim (T) to Chamfer (C) and use the same 25 value. Make a single LMB pick on another 90-degree corner. The length of the chamfer should be 25mil, as shown in the right image below:

![]()

Enable the setting Set trim size by cursor:

![]()

Select another vertex location and adjust the chamfer by moving your cursor:

![]()

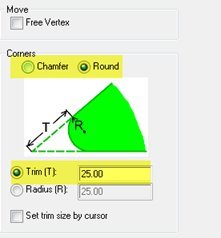

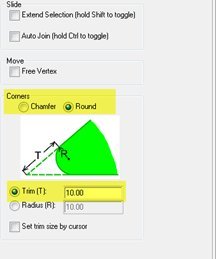

Rounding Corners

Adjust the settings as shown in the figure below, with corners now set to “round”. Disable the setting “Set trim size by cursor”:

![]()

Hover over a corner vertex location then use RMB – Trim Vertex:

![]()

Change the setting to Radius (R) = 25:

![]()

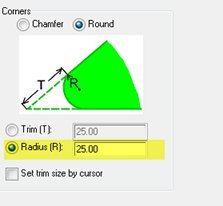

Make a LMB pick on another 90-degree corner to create a 25mil radius, continue changing corner types as you please. Round the upper route corner of the route keepout shape:

![]()

Chamfering All Corners

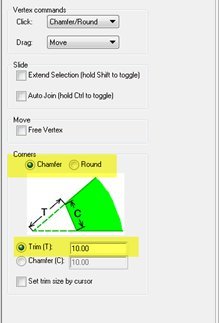

Adjust settings as shown in the figure below:

![]()

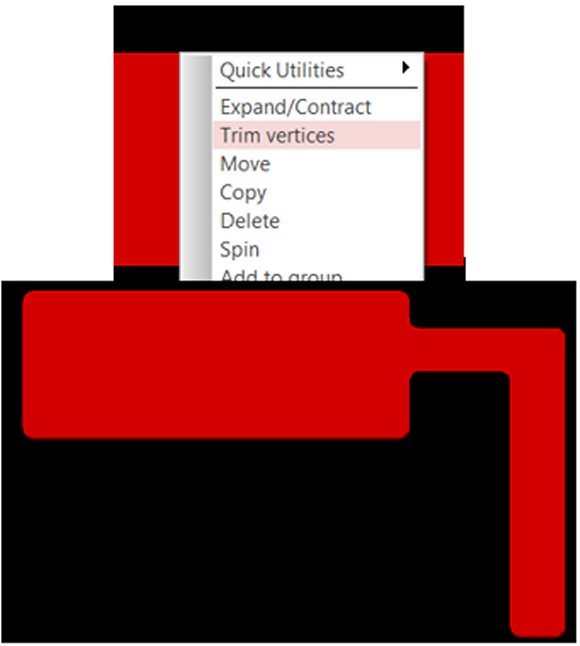

Hover over a line segment associated with the shape, then RMB – Shape – Trim vertices:

![]()

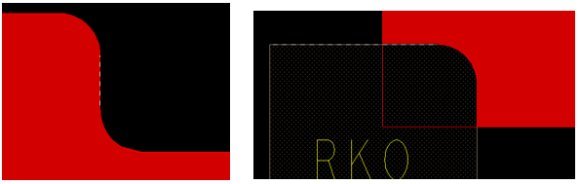

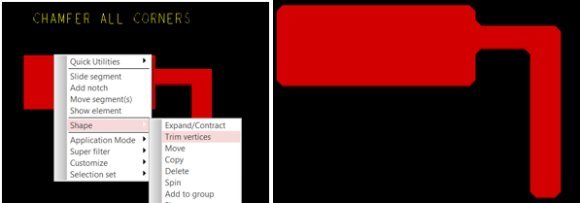

Rounding All Corners

Adjust the settings as shown below:

![]()

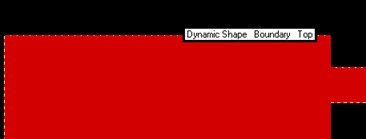

Hover over the shape boundary, then use Tab key to ensure “shape outline” is active. Note the datatip display of “Dynamic Shape Boundary”:

![]()

While hovering over the boundary, use the RMB to access the Trim vertices command. This is the second command in the list:

![]()

Joining Segments

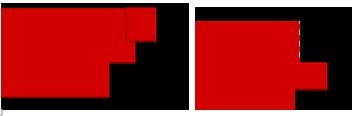

Adjust settings as shown in the figure below. Select the upper right vertical segment and slide to the left noting the behavior. Undo or Oops to revert back to original shape:

![]()

![]()

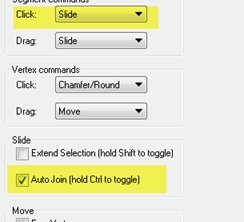

To join the segments, enable the Auto-Join setting as shown below. You can also use the CONTROL key to toggle the state of the setting:

![]()

Select the same vertical segment and slide to the left, noting the joining behavior with the adjacent segments. If you experience an issue performing this step, click the Tab key to ensure you are acting on a segment and not the shape boundary. This should be the final result of your editing:

![]()

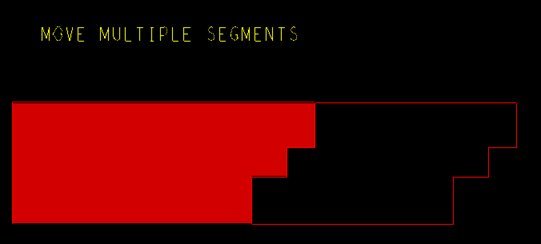

Sliding Multiple Segments

The goal of this step is the slide the entire right edge to the right while maintaining existing segment construction:

![]()

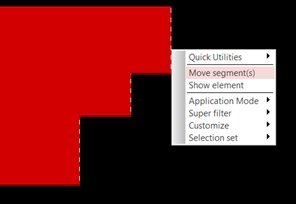

Select the three vertical segments on the right side of the shape. You can do this by depressing the SHIFT key, then make three individual selections. Hover over any one segment then use the RMB to access the Move Segments command:

![]()

Move the group of segments to the right.

I look forward to your comments!

Jerry “GenPart” Grzenia

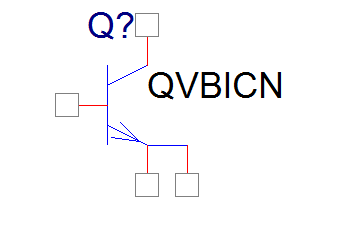

![]()

![]()