Switched Mode Power Supplies (SMPS) are used extensively in most of the power conversion processes due to their efficiency and compactness. The analysis, design, and the modeling processes have all grown in the past four decades. Most of these developments were centered on hard-switching converters where the switching frequency was limited to a few KHz. The present direction of evolution in SMPS is towards high efficiency and higher power conversion density. These twin objectives demand high switching frequency and low overall losses. The designing and testing of SMPS is cumbersome work and require lots of trial and error methods to get the right output.

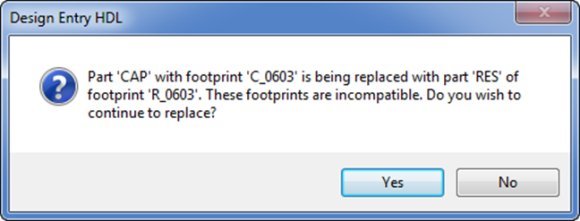

Allegro AMS Simulator (PSpice) gives you an option to reduce your effort by simulating your design before going for the real hardware design. The following is an excerpt from an app note* that provides details on designing and simulating SMPS using AMS Simulator with a real-time test circuit.

Introduction

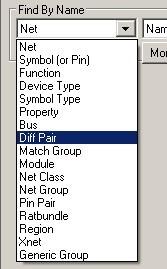

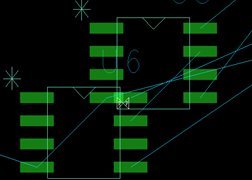

The full-bridge topology of the DC-to-DC power transformer is an electrical bridge between the junctions of four MOSFETs, M8, M9, M10, and M11, as shown in Figure 1.

![]()

Figure 1: Full-Bridge DC-to-DC Converter

MOSFETs M8 and M11 are switched on simultaneously for an adjustable time during one half period. MOSFETs M9 and M10 are switched on simultaneously for an equal time during the alternate half period. The transformer primary voltage is a square wave DC voltage supply.

Topologies vary as per the desired output voltages, for various power ranges. Multiple switch topologies are generally used for high-output power applications. These switched-mode power supplies operate in the frequency of a few KHz to MHz range. There is a growing trend of increasing the switching frequency.

Circuit Analysis

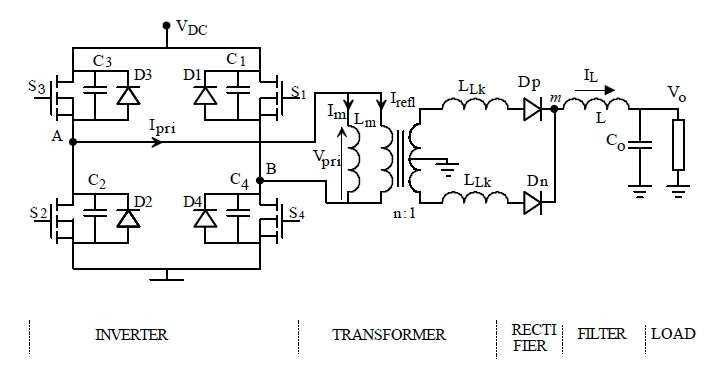

Figure 2 shows a schematic diagram of a full-bridge DC-to-DC converter used for analysis and simulation. Capacitors C1 to C4 represent the output capacitances of the MOSFET including any external snubber capacitors that are added. Lm and LLk represent the magnetizing and leakage inductances, respectively, of the transformer.

![]()

Figure 2: Schematic Diagram of Full-Bridge DC-to-DC Converter

For the purpose of analysis, a complete cycle of operation is divided into eight distinct intervals for the inverter. These cycles are covered in detail in the app note*.

Sample Circuit and Simulation Results

Specification:

- Input voltage: 27V

- Output voltage: 270V

- Output power: 400W

- Output load: 1.5Amp

- Switching frequency (fs): 50KHz

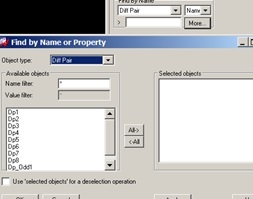

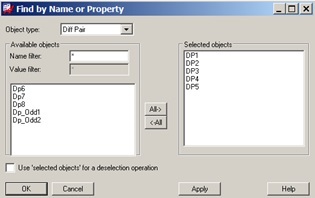

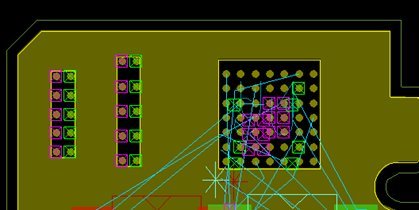

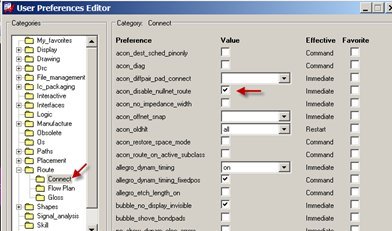

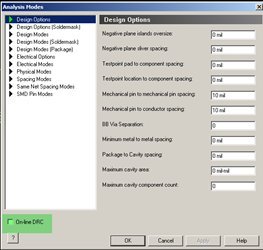

Design Process

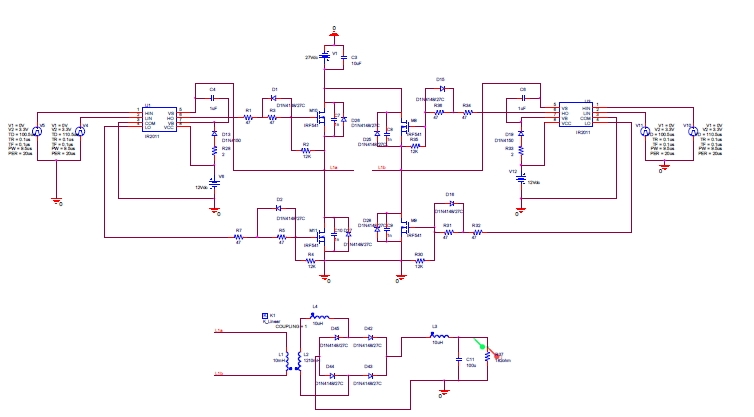

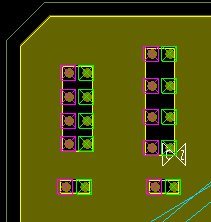

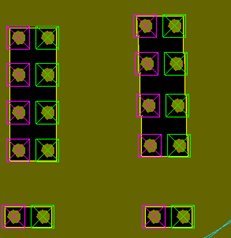

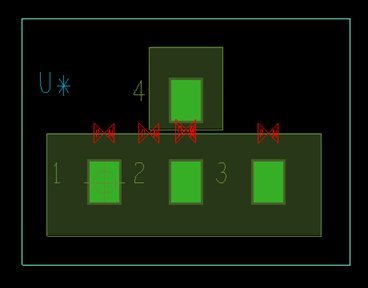

A schematic diagram of the power converter is shown in Figure 3.

An input of 27V DC is given to the full-bridge converter. Switching the action of the inverter will apply voltages of +/-27V to the primary of the high-frequency transformer during each half cycle. The transformer operates at a frequency of 50KHz. IR2011, used as gate driver, is a high-power, high-speed MOSFET driver that has a floating channel up to 200V and a gate driver supply voltage range of 10V to 20V. It has a matched propagation delay for both channels. IRF541 MOSFET meets the voltage and current requirements for the bridge switches. It has the output capacitance COSS of 800pF and an RDS (ON) of 0.085.The drain to source breakdown voltage is 60V. IRF541 also has low driving requirements, high power dissipation, and a high-operating switching frequency.

A fast recovery diode from Microsemi, D1N4148 is chosen for the main rectifier because of its low forward voltage drop of 0.3V.The transformer is designed using two inductors: L1 and L2 are coupled together with coupling constant K linear having a coupling coefficient of 1.0. Input voltage across the primary is +/-27V and the output voltage is 270V.

Due to the voltage drop across the MOSFET and rectifier diodes, the turn ratio can be considered as 11. If the primary magnetizing inductance is considered as 10mH, secondary coil inductance will be 1210mH. A leakage inductance of 10uH is considered for the transformer.The load resistance Rl= (270*270)/400 = 182Ω.

![]()

Figure 3: Full-Bridge DC-to-DC Converter

U1 and U3 are gate drivers and M8, M9, M10, and M11 are MOSFET switches. D42, D43, D44, and D45 form the bridge rectifier circuit at the transformer coil secondary. L4 is the leakage inductance of transformer. L3 and C11 form the filter circuit, which reduces the ripple of 270V DC at the output.

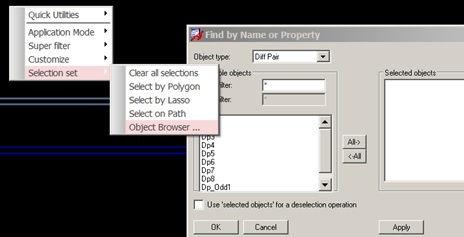

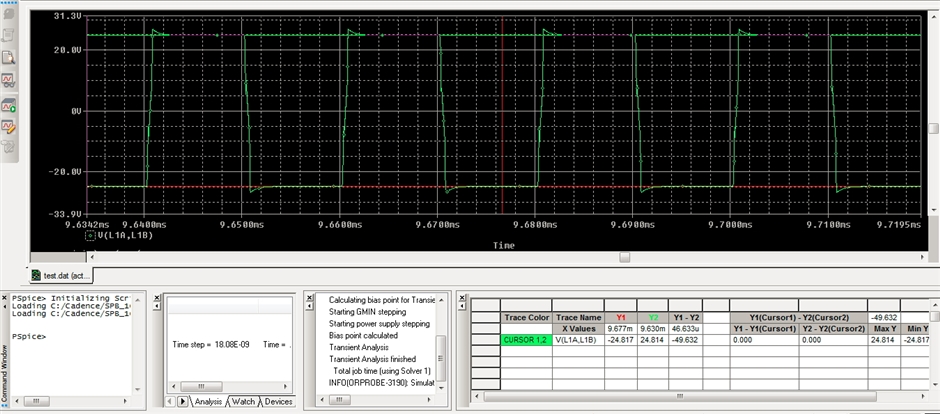

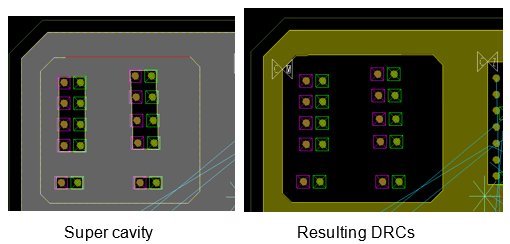

Simulation Results

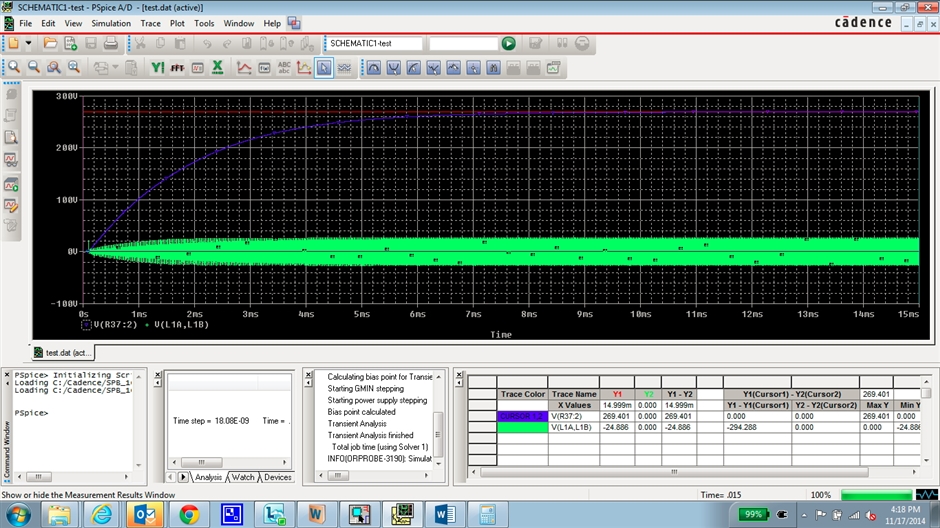

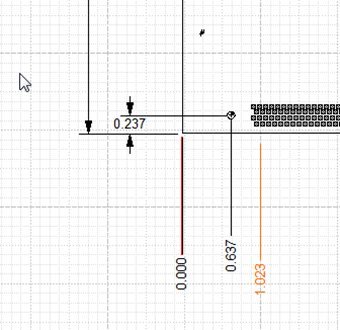

The voltage across the primary coil (L1a and L1b) will be a few voltages less than the specified input DC voltage, due to the voltage drop across the MOSFETs. Simulation results show the primary voltage as +/-24.8V (peak).

![]()

Figure 4: Voltage Across Primary Coils L1a and L1b

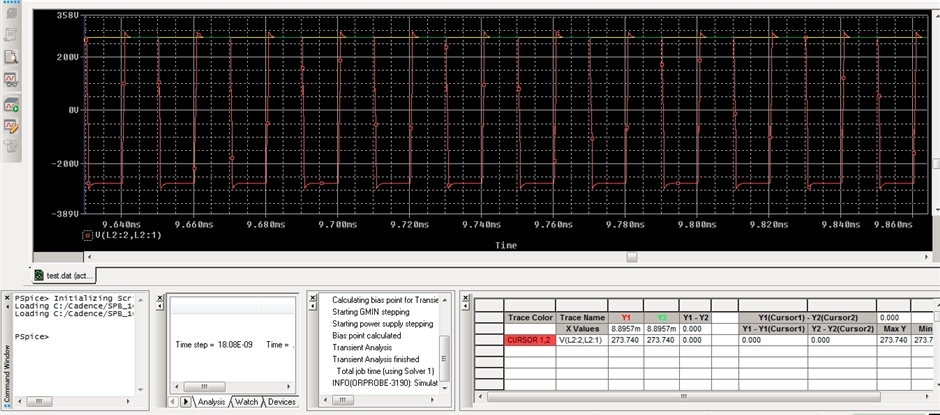

The secondary voltage will be around +/-273V (peak), since the turn ratio is considered as 11.

Simulation results show the secondary voltage as 273.74V (peak).

![]()

Figure 5: Voltage Across Secondary Coil

There would be a voltage drop across the rectifier diode. Simulation results show 269.4V DC at the output (R37).

![]()

Figure 6: Voltage Across Primary Coil (Green) and Load (Blue)

Refer to the complete app note* for a detailed procedure about each of the cycles described above and the necessary steps involved in the process.

* Note: The app note link can only be accessed by Cadence customers who have valid login credentials for Cadence Online Support (http://support.cadence.com).

Naveen Konchada

![]()

![]()